Raja Koduri氏、Hot Chipsで4タイルのXe HP GPU「Petaflops Scale」を公開

ここ数ヶ月間、IntelのRaja Koduri氏は、次期Xeグラフィックスのアーキテクチャとラインアップの一部をゆっくりと明らかにしてきた。Xeファミリーは、Xe LP Graphicsブランドの低消費電力統合型やエントリーレベルのグラフィックスソリューションから、ダイスタッキングを備えたデータセンター用マルチチップソリューションまで、あらゆるものを網羅します。

先週も触れたように、IntelのXe HP Graphicsには3つのバリエーションが用意されます。これまで何度か紹介してきたベースモデルは、シングルタイルで512EU(Execution Units)を搭載し、HMB2eスタックを2つ搭載する可能性が高いです。Intelは正確なスペックを確認していないが、1タイル、2タイル、4タイルの各バリアントの計算ワークロードに対するパフォーマンスのスケーリングを示しました。

追加のタイルによるスケーリングは、ほぼ完璧すぎるように見えるかもしれませんが、これはリアルタイムグラフィックスのワークロードではないことに注意してください。SLIやCrossFireのような技術では、GPU間で作業を分割することははるかに難しく、追加のGPUからのスケーリングでは、通常、ゲーマーはせいぜい50~80%のパフォーマンスしか得られません。しかし、計算ワークロードの場合は、タスクが独立していることが多いため、完璧なスケーリングが可能です。

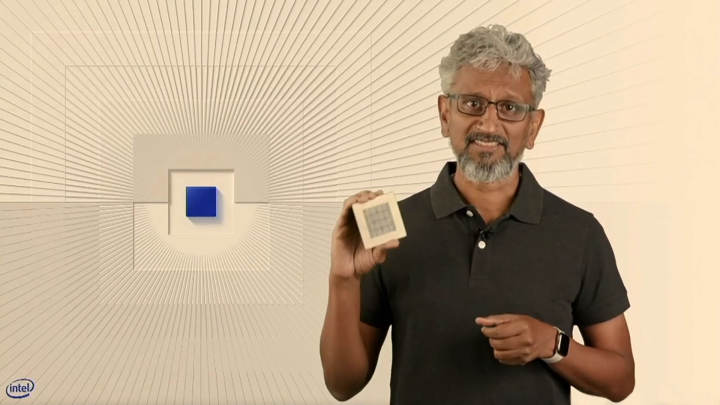

4層GPUは実際には存在せず、単なる売名行為に過ぎないと疑われないように、Raja 氏はHot Chipsのプレゼンテーション中に大きなパッケージを取り出し、カメラに向かって簡単に展示しました。そう、これまで見てきたどのパッケージよりもずっと大きいのです。

4層構造のXe HPが生産されるのか、それともIntelがXe HPC、別名Ponte Vecchioを準備している間のテスト製品に過ぎないのかは、また別の問題です。

Xe HPは、EMIBを使ってマルチタイル構成にスケールするだけです。Xe HPCでは、Rambo Cacheタイル、Foverosダイスタッキング、Co-EMIBを追加強化したものも用意される予定です。Ponte Vecchioは、次期Auroraスーパーコンピュータでの使用が計画されており、現在遅れているIntelの7nmリソグラフィで製造されることになっていました。

その間、Intelは現在、1タイル、2タイル、4タイルのXe HPシリコンをラボに持っています。ご想像の通り、EMIBリンクにより、後者の2つのパッケージは基本的にベースデザインの2倍と4倍のサイズになるため、GPUには3つの別々のソケットが必要になります。

Xe HP Raja氏が披露した4タイルの実装では、約42TFLOPSのFP32コンピュートが可能です。しかし、実際にはそれが最大能力ではないです。Raja氏はまた、4タイルチップは「ペタフロップス規模のコンピューティング」、つまり1000TFLOPS以上に達することができるとも述べました。これは、正確な構成はわからないが、テンソルコアの存在のおかげです。

NvidiaのA100アーキテクチャやGoogleのTPUv4のように、Xe HPはテンソルコアをサポートします。テンソルコアは1サイクルあたり128回の動作が可能で、EUあたり1つのテンソルコアを搭載していると想定しています。2048個のEUを使用すると、以下のようになります。

2048 × 128 × 2 (FMA) = 524,288

クロック速度が足りないので、1 ペタフロップで 2GHz のベースラインか、1クロックあたり128OPS以上の演算が可能な別のテンソルコアの配置が必要になるかもしれません。いずれにしても、スーパーコンピュータが超大規模コンピューティングのレベルに到達するのがはるかに容易になるはずです。

関連ニュース

Tom's Hardware・2022-06-03

Tom's Hardware・2022-06-01

Tom's Hardware・2022-05-30

Tom's Hardware・2022-05-23

Tom's Hardware・2022-05-23

Tom's Hardware・2022-05-19

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)