Intel、HBM搭載のマルチチップレットCPU「Sapphire Rapids」を発表

インテルは昨年末、一部の第4世代Xeon Scalable「Sapphire Rapids」プロセッサにオンパッケージのHBMメモリを搭載することを正式に確認しましたが、同社はこれまでHBMを搭載した実際のCPUのデモンストレーションや、DRAM構成を明らかにしていませんでした。今週初めに開催されたIMAPS主催のInternational Symposium on Microelectronicsで、同社はようやくHBMを搭載したプロセッサを展示し、マルチチップレット設計であることを確認しました。

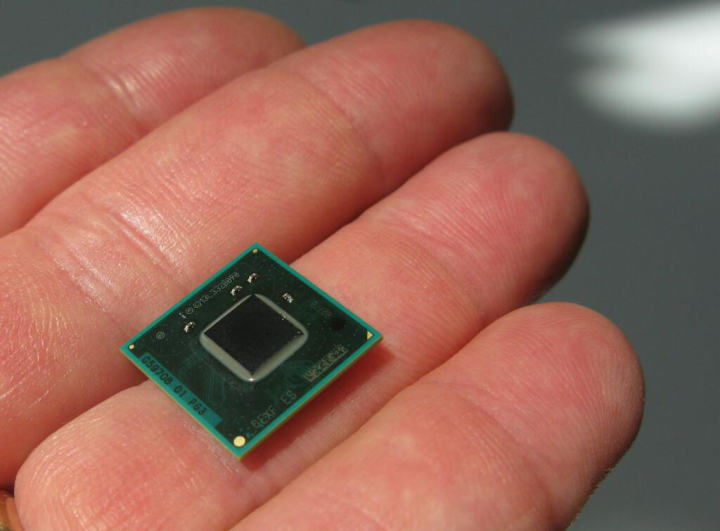

Intelは、Sapphire RapidsプロセッサがHBM(おそらくHBM2E)とDDR5メモリをサポートし、メインのDDR5メモリと併用してもしなくてもHBMを使用できることを何度も確認していましたが、今週になるまで、実際にHBMを搭載したCPUを展示することはありませんでした(Tom Wassick/@wassicktが公開した写真のおかげです)。

その結果、4つのSapphire Rapidsチップレットのそれぞれに、2つの1024ビットインターフェース(つまり、2048ビットのメモリバス)を使用する2つのHBMメモリスタックが搭載されることがわかりました。正式には、JEDECのHBM2E仕様は3.2GT/sのデータ転送速度を上限としますが、昨年、SK Hynix社は3.6GT/sの動作に対応した16GBの1024ピンのKGSD(known-good stacked die)の量産を開始しました。

Intel社がこのようなKGSDの使用を選択した場合、HBM2EメモリはSapphire Rapids CPUに3.68TB/sという驚異的なピークメモリ帯域幅(ダイあたり921.6GB/s)を提供することになりますが、128GBのメモリにしか対応していません。 一方、SPRの8つのDDR5-4800メモリチャネルは、チャネルごとに1つのモジュールをサポートし、307.2GB/sを提供するため、最近発表されたSamsungの512GB DDR5 RDIMMモジュールを使用して、少なくとも4TBのメモリをサポートします。

また、HBMを搭載したSapphire Rapidsは、大型のBGAフォームファクタを採用し、マザーボードに直接ハンダ付けされることも注目すべき点です。IntelのLGA4677フォームファクタはかなり狭く、CPUのパッケージ上にはHBMスタックのための十分なスペースがないため、これは特に驚くことではありません。

さらに、HBMのような非常に高性能なメモリサブシステムを必要とするプロセッサは、高クロックで動作するコアを多数搭載し、TDPが非常に高くなる傾向があります。また、HBMのような高性能なメモリサブシステムを必要とするプロセッサは、高クロックで動作するコアを搭載し、TDPも非常に高くなります。したがって、HBMを搭載したSPRは、(インテルの最大56コアのCPU「Xeon Scalable 9200」のように)一部の顧客にしか提供されず、ほとんどがスーパーコンピュータ向けになると思われます。

もうひとつ注目すべき点は、画像上のSPRチップレットの形状が正方形ではなく長方形であることです(LGA4677パッケージのSapphire Rapidsの初期の画像と同様)。この画像の作者は、"Intelの従業員から渡されたSPRと書かれたチャートからのもので、口頭ではSapphire Rapidsと記されていた "と述べました。つまり、HBMをサポートするSapphire Rapids CPUは、通常のSPRプロセッサとは異なるチップレット構成になる可能性があるようです(結局、通常のXeon Scalable CPUには、ダイスペースを取るHBMインターフェイスは必要ありません)。

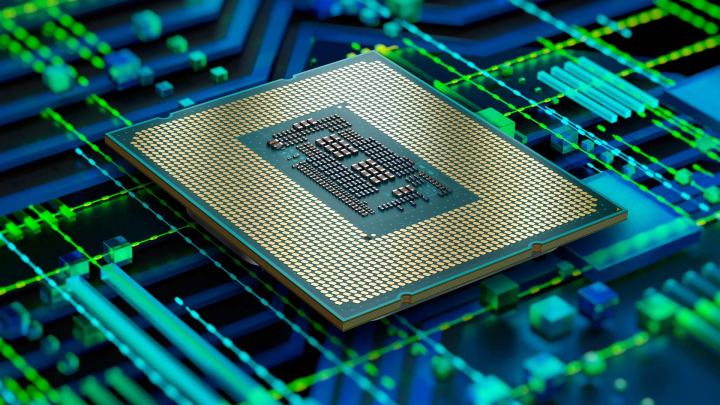

インテルのSapphire Rapidsプロセッサーは、PCIe Gen 5のサポートとその上のアクセラレータ用のCXL 1.1プロトコル、DDR5とHBMをサポートするハイブリッド・メモリー・サブシステム、インテルのAdvanced Matrix Extensions(AMX)に加え、データセンターやスーパーコンピュータのワークロード用に設計されたAVX512_BF16およびAVX512_VP2INTERSECT命令、インテルのData Streaming Accelerator(DSA)テクノロジーなど、数多くの新技術を搭載します。

今年の初め、インテルのSapphire Rapidsは、モノリシック型の従来製品とは異なり、ダイ間にEMIBインターコネクトを備えたマルチチップパッケージを採用することがわかりました。コアの数は歩留まりと電力に左右されるものだが(一部の報道ではSPRは最大56のアクティブコアを搭載するとされるが、実際のチップレットには80ものコアが搭載される可能性がある)、第4世代Xeon ScalableがIntelの最新のパッケージ技術とデザインパラダイムを採用した最初の製品となることは明らかです。

関連ニュース

Tom's Hardware・2022-06-03

Tom's Hardware・2022-06-03

Tom's Hardware・2022-06-03

Tom's Hardware・2022-06-01

Tom's Hardware・2022-05-31

Tom's Hardware・2022-05-31

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)