AMD、新しい3D V-Cache搭載Ryzenチップを公開、チップあたり最大192MBのL3キャッシュを搭載し、15%のゲーム向上を実現

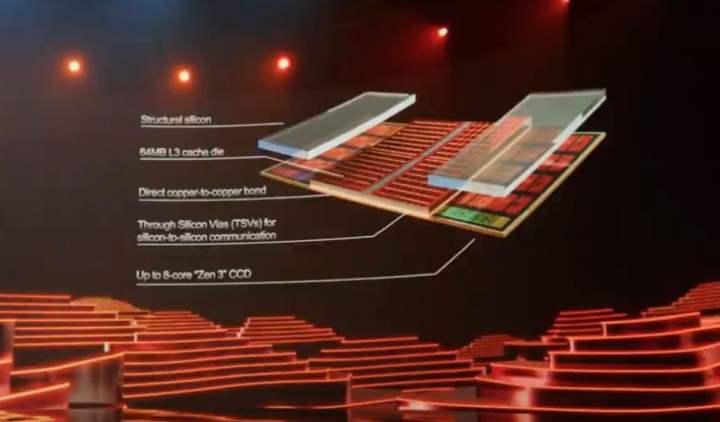

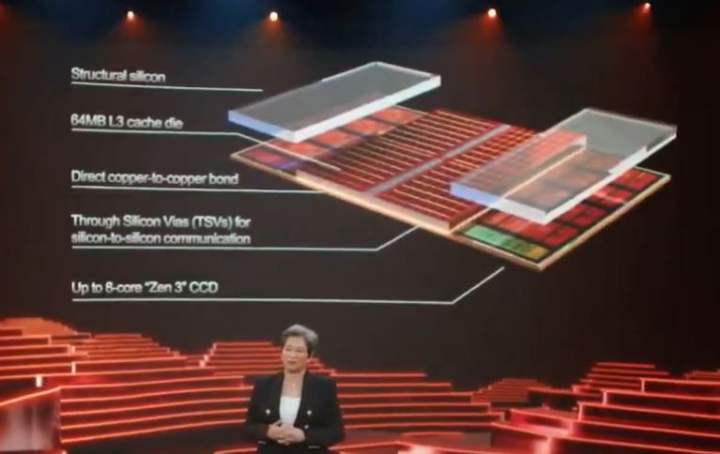

AMDはゲームを完全に変えてしまいました。AMDは2021年のComputexで驚くべき情報を公開しました-同社は、今年から生産を開始するZen 3アーキテクチャをベースにした3Dスタック型のチップレットを持っています。これらの革新的な新しいチップレットは、64MBの7nm SRAMキャッシュ(3D V-Cacheと呼ばれる)をコアコンプレックスダイ(CCD)の上に垂直に追加積層し、CPUコア用のL3キャッシュの量を3倍にします。この技術により、Ryzenチップ1個あたり最大192MBのL3キャッシュを搭載することができ、現在の上限である64MBを大幅に上回ることができます。

また、AMDのCEOであるリサ・スーは、同社がすでに稼働させているRyzen 9 5900Xチップのプロトタイプを披露し、新アーキテクチャーによるゲームプレイの高速化について、かなり印象的なデモを行いました。これは、通常、新しいCPUマイクロアーキテクチャやプロセスノードを採用した場合に得られる値ですが、AMDは、すでに標準的なRyzen 5000モデルに搭載されているのと同じ7nmノードとZen 3アーキテクチャを用いて成果を達成しました。

AMDは、Ryzen CCDの上部に3DキャッシュをTSV(Through Silicon Via)で接合し、チップとキャッシュの間に最大2TB/sの帯域幅を確保します。この技術は、こちらで紹介したTSMCの3DFabric技術の提供によるものです。

また、AMDは、3Dキャッシュダイを薄くし、チップに構造用シリコンを追加することで、最終的に通常のチップと同じ外観のRyzenプロセッサーを実現しました。

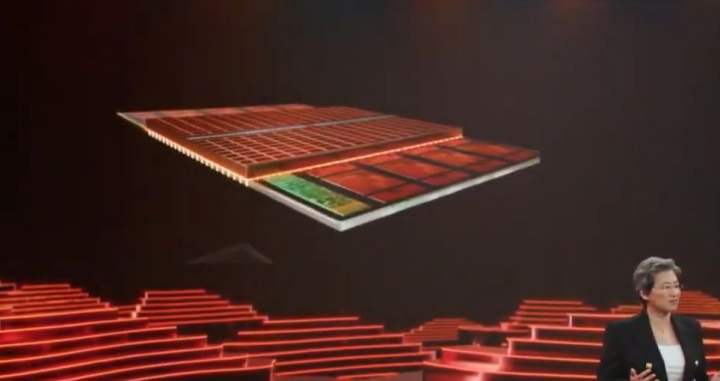

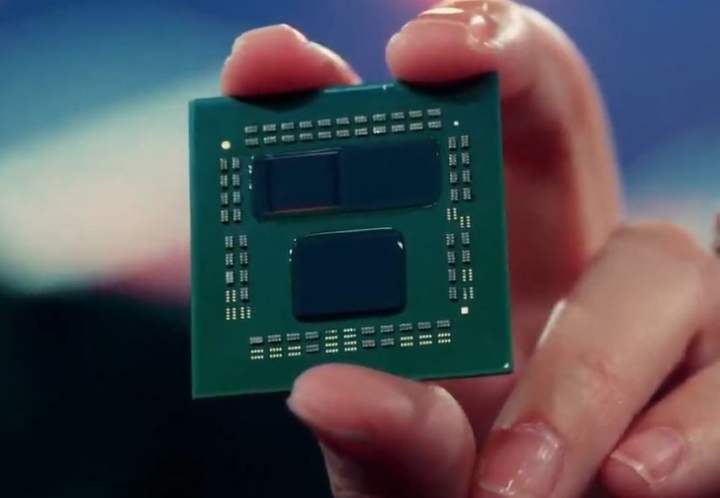

Su氏は、3Dチップレット技術がすでに注入されたRyzen 9 5900Xのプロトタイプを披露しました。6×6mmのハイブリッドSRAMがチップレットの上部に接着されているのがわかります(上の画像の左チップレット)。完成したデバイスには、CCDあたり96MBのキャッシュが搭載され、12コアまたは16コアのRyzen 5000プロセッサーでは、合計192MBという非常に大きなL3キャッシュが搭載されることになります。

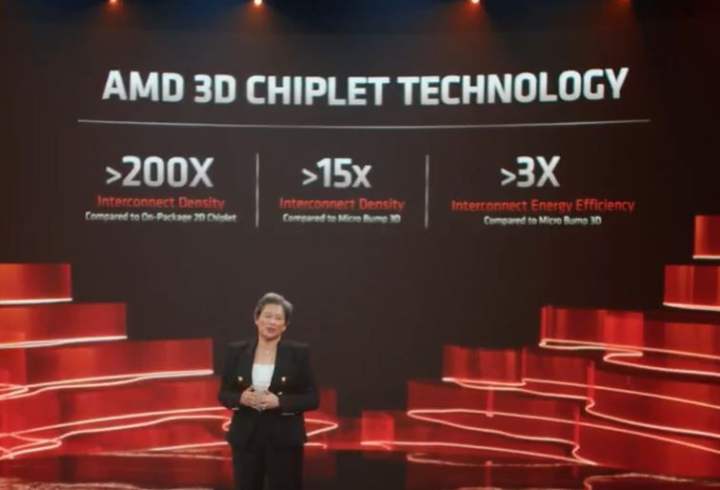

AMDは、TSVを用いたハイブリッド・ボンド・アプローチを採用し、2Dチップレットの200倍以上のインターコネクト密度、マイクロバンプを用いた3D実装と比較して15倍のインターコネクト密度、そして3倍のインターコネクト・エネルギー効率を実現しました。

スーは、これらの驚異的な進歩は、マイクロバンプのないダイからダイへのインターフェースが、銅と銅を直接接合することで、熱伝導、密度、配線ピッチを改善し、さらにエネルギー効率も飛躍的に向上させたことによるものだと述べました。このような特性の組み合わせにより、このアプローチは世界で最も効率的な3Dインターコネクト技術になるとスーは述べました。

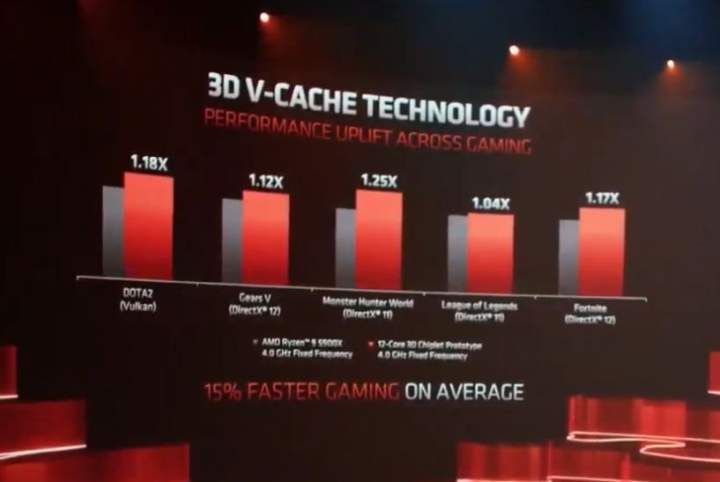

Su氏は、新しい3D V-Cacheを搭載したRyzen 9 5900Xのプロトタイプと、標準の5900Xを比較し、両チップのクロックスピードを4.0GHzに固定してデモを行いました。3Dプロトタイプでは、トリプルAタイトルの「Gears 5」で12%の向上が見られました。

その結果、3D V-Cacheテクノロジーを搭載したRyzen 9 5900Xは、1080pで動作するさまざまなゲームにおいて、平均15%のパフォーマンス向上を実現しました。Dota 2、Monster Hunter World、League of Legends、Fortniteなどのタイトルがそれにあたります。

このキャッシュは、通常のL3キャッシュよりもレイテンシーが高く、ソフトウェアの最適化が必要なのではないかなど、疑問は山ほどあります。

スーは、年末には3Dチップレットを搭載した「最上位製品」での生産開始の準備が整うと述べました。これは積層技術の最初の実装に過ぎず、AMDは将来的に他の機能にもこの技術を使用することができます。AMDは将来的に他の機能にも使用することができます。

関連ニュース

Tom's Hardware・2022-06-01

Tom's Hardware・2022-05-31

Tom's Hardware・2022-05-30

Tom's Hardware・2022-03-03

Tom's Hardware・2022-02-22

Tom's Hardware・2022-02-18

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)