4層構造の3D積層技術で未来のチップを実現

IME(Institute of Microeletronics)の研究者たちは、最大4つの半導体層を積み重ねることができる技術的なブレークスルーを達成しました。これにより、従来の2D製造技術と比較して最大50%のコスト削減が可能となり、この技術は将来の最高のCPUや最高のグラフィックカードに使用されることになるでしょう。

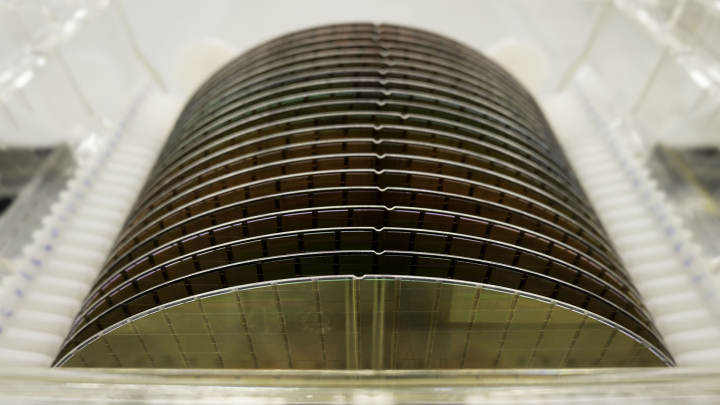

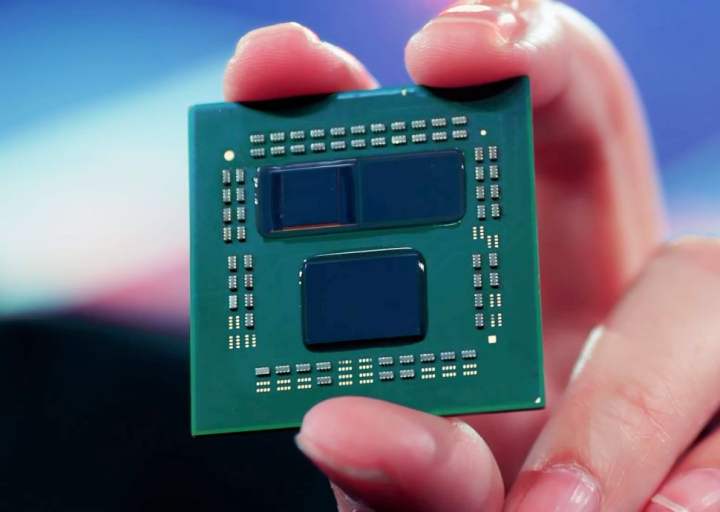

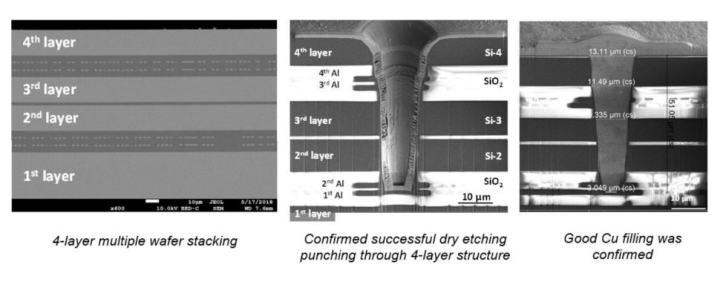

この技術は、AMD社が発表したTSMC社のSRAM積層技術に比べてステップアップしています。このプロセスでは、現在のところ2つのダイ(AMD社の場合、1層目にZen 3 CCX、2層目に96MBのSRAMキャッシュ)しか接合できません。IMEの研究者たちは、TSV(Through Silicon Vias)を介して4つの異なるシリコン層を接合することに成功したプロセスを発表しました。

TSVとそれを可能にするアクティブなウェハースタッキングは、ムーアの法則を維持(さらには改善)するための最も重要な技術的ブレイクスルーの1つとして評価されます。これは、性能目標を達成するために極端に高い周波数で動作する必要のない、より広い情報バスを可能にするからです。これにより、従来は水平に配置されていた部品を垂直に積み重ねることができるようになり、設計の高密度化が可能になりました。また、電力効率の向上や放熱の効率化、さらには歩留まりの向上にもつながります。例えば、CPUを構成するさまざまな部品は、従来のモノリシック方式ではなく、異なるウェハーで製造することができるため、製造上の欠陥に対する耐性が自動的に向上します。

IMEの製造方法は、"Face-to-FaceとBack-to-Backのウェハ接合と、積層後のワンステップTSVの組み合わせ "です。これは、ベースとなる第1層の「面」が第2層と向き合い、第2層の「裏」が第3層の「裏」と向き合い、さらに第4層の「面」と向き合うというものです。IMEは、これらの層を接着した後、設計された経路に沿ってエッチングを行い、最終的にデータが流れるTSVとなるように「パンチング」を行いました。

垂直方向に伸びると、効率は上がっても放熱性が悪くなるのではないかと思われるかもしれませんが、その通りです。だからこそ、(現在では)異例ともいえるダイへの直接冷却技術が開発されているのです。データキューブはもうすぐ単なるSFではなくなるでしょう。

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)