Nvidia、将来のGPUのための対面式3Dスタックダイの特許を取得

半導体メーカーはこれまで、従来のモノリシックなGPUダイ設計から脱却する方法を模索してきました。それは、製造コストを抑えながら、より優れた性能のスケーリングを可能にするものです。Nvidiaは、TSV(Through Silicon Via)技術を用いた3Dダイスタッキングを導入し、電力供給を強化することで、問題を解決しようとします。これは、すでにAMD、Intel、TSMCから発表された技術と似ているように聞こえますが、いくつかの違いがあります。

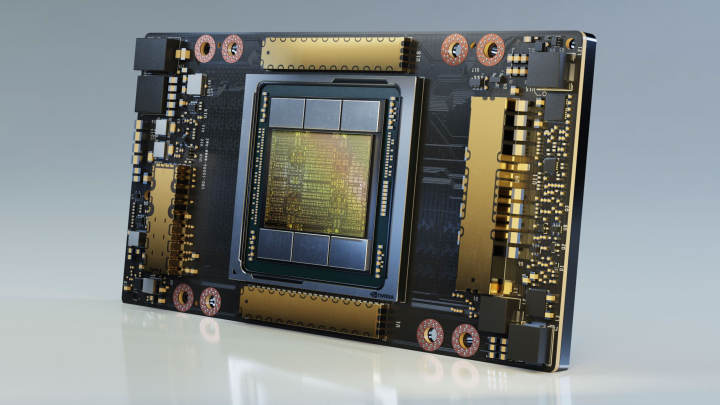

Nvidiaがモノリシック・ダイ・デザインからの脱却を計画していることはすでに知られています。同社は、さまざまなパッケージング技術を使ってより高い性能を得る方法を積極的に模索しており、最近では、マルチチップモジュール(MCM)を使って、継続的な性能スケーラビリティを持つGPUを構築しています。

遡ること2017年、NvidiaはMCM-GPUの設計を「International Symposium on Computer Architecture(ISCA)」で発表しました。Nvidiaは、複数のダイのロジックを使って膨大な量のコアを相互に接続し、コストを管理しながら継続的に性能を向上させた新しいGPUを開発する計画でした。GPUのダイが大きくなると、コストは指数関数的に増加するため、相互に接続されたいくつかの小さなダイを作ることが、よりコスト効率の高いソリューションとなります。MCM-GPUのパッケージング手法は、複数のダイを接続することで、大幅な性能向上を実現し、問題を解決します。

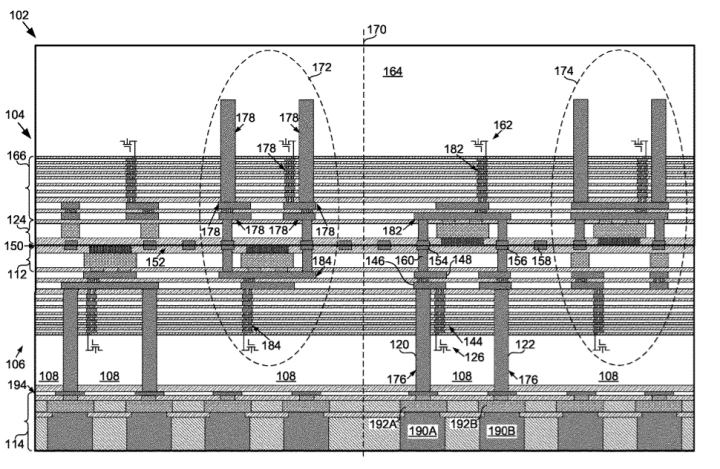

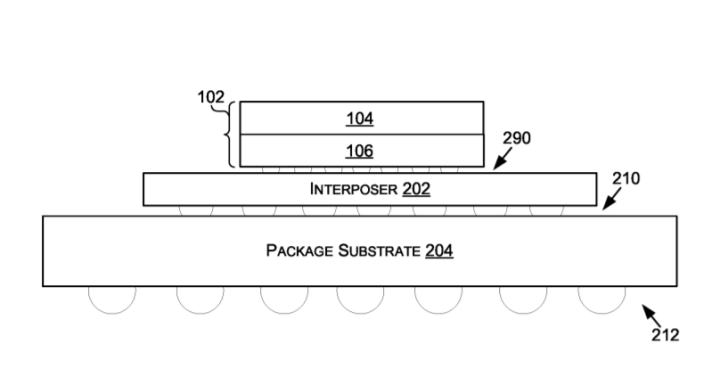

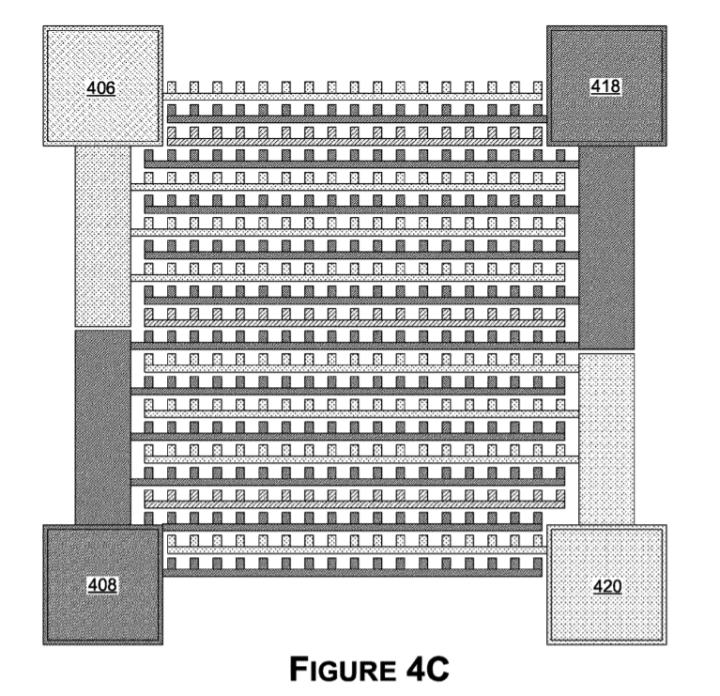

チップの設計は2次元的なスケーリングに限定されるものではなく、Nvidiaが今日特許を取得したのもそのためです。「Face-to-face dies with enhanced power delivery using extended TSVs」と名付けられたこの特許は、半導体のダイを3次元的に積み重ねることを提案するもので、特に長いシリコン貫通型ビア(TSV)を使って電力供給を強化することに注目します。

この方法では、まずベースとなるダイの表面にプローブパッドを置いてテストを行います。その後、第1のダイの表面にインターフェース層を形成し、すでに存在するプローブパッドの上に重ねます。最後に、第2のダイを取り出して、インターフェース層の上にマウントし、ダイ間のインターフェースのパッドを他のダイの補完的な接続部に接続します。これにより、ダイ同士が対面して実装され、3Dチップが誕生します。

Nvidiaの特許は、超長尺のTSVを用いた電力供給の強化に焦点を当てています。このようにダイを重ねることで、ロジック(処理コア)からメモリーまでを接続することができます。通常、メモリの接続にはそれほど電力を必要としませんので、電力供給の強化ということは、Nvidiaがプロセッシングコアのスタッキングを行い、3Dプロセッサの演算重視のアプローチを計画しているのではないかと考えられます。

もちろん、特許を申請したからといって、実際の製品にその技術を使わなければならないわけではありません。企業が発明を特許化するのは、他の企業が特許を取得できないようにするためであったり、将来の製品のためのプレースホルダーとしてであったりします。いずれにしても、MCM-GPU方式が登場することはすでにわかっており、Hopperのような次世代GPUアーキテクチャの中には、3Dダイスタッキングのメリットを活かして競争力を高めるものもあるでしょう。

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)