Intelは、Sapphire Rapidsのパッケージ上でHBMメモリサポートを確認します

新年の数日前にリリースされたドキュメントで、Intelは、Sapphire Rapidsマイクロアーキテクチャに基づく今後のXeonスケーラブルプロセッサがオンパッケージHBMメモリを対応することを確認しました。HBMを搭載したメモリサブシステムは、DDR4やDDR5などの従来のタイプのメモリを使用するサブシステムと比較して、CPUが利用できる帯域幅を大幅に増やします。つまり、将来のCPUは、同じパッケージに大量のHBMメモリを搭載した今日のGPUに似ている可能性があります。

HBMサポートが確認されました

IntelがHBMメモリサポートでSapphire Rapidsを強化する可能性があることを示唆する噂がここ数ヶ月で出てきました。 Intelは、命令セット拡張機能と将来の機能プログラミングリファレンス(@ InstLatX64 / Twitterによって発見された)の第42版で、Sapphire RapidsがHBMメモリを対応することを確認しました。

ドキュメントの第15章では、Sapphire Rapidsマイクロアーキテクチャを搭載した将来のCPUのマシンエラーコードを定義し、セクション15.1では、将来のプロセッサの統合メモリコントローラに関連するエラーコードについて具体的に説明します。この章では、HBMコマンド/アドレスパリティエラーおよびHBMデータパリティエラーのエラーコードについて詳しく説明します。これは、基本的に、Sapphire RapidsがHBMタイプのメモリを処理できることを意味します。

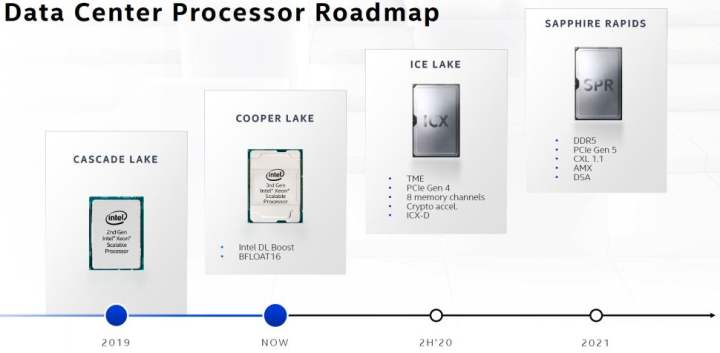

これまでのところ、Intelは、Sapphire Rapidsプロセッサがデータストリーミングアクセラレータ(DSA)テクノロジで強化された8チャネルDDR5メモリコントローラを備えていることを公式に確認しました。これにより、今日のDDR4ベースのメモリサブシステムよりも大幅に帯域幅が拡張されます。さらに、このチップはIntelの次世代Optaneメモリモジュールを対応します。

詳細は不明のまま

さまざまなCPUアーキテクトがマイクロプロセッサのオンボードHBM対応を長い間想定してきたため、Sapphire Rapidsに追加することは必ずしも画期的な概念ではありません。残っているのは、IntelがオンボードHBMの実装をどのように計画しているか、そしてどのように使用するかです。

世界最速のスーパーコンピューターである富岳に搭載されている富士通の48コアA64FXプロセッサは、32GBのHBM2メモリを搭載しており、実際にはDDR4メモリを対応しているようには見えません。 A64FXチップは、高性能GPUで見られるのと同じ方法で、インターポーザーを使用してHBM2に接続します。

対照的に、AMDのX3DおよびIntelのFoveros 3Dスタッキングテクノロジーにより、これらの企業はチップレットと他のタイプのダイ(メモリデバイスなど)を互いに積み重ねてチップを小さくすることができます。残念ながら、IntelはSapphire RapidsにFoverosを使用する予定があるかどうかについて公に話したことはありません。

さらに重要なのは、IntelがSapphire RapidsでHBMをどのように使用するかです。一部の製品では、DDR5の代わりにHBMを使用できます。これらのCPUモデルは、DDR5対応のモデルほど多くのメモリをサポートしませんが、代わりに大規模な帯域幅を提供します。また、多くの電力を消費するため、製造元は特定のアプリケーションのみを対象とする場合があります。

Intelは、HBMとDDR5(または場合によってはOptaneメモリ)の両方で構成されるハイブリッドメモリサブシステムを構築して、両方を最大限に活用することもできます。この場合、HBMはCPUとDDR5の間にある大規模なキャッシュのように機能します。歴史的に、AMDとIntelはどちらもオフチップキャッシュを使用してきたため、まったく新しい概念ではありません。一方、電力が制約となり、HBMを伝送する可能性のあるSKUの数が制限される可能性があります。

たくさんの革新

IntelのSapphire Rapidsプロセッサは、今後のIce Lake-SPチップを超えるパフォーマンスと機能の点でかなり大きな飛躍を約束します。

データセンターやスーパーコンピューターのワークロード用に設計されたAVX512_BF16とAVX512_VP2INTERSECT命令と同様に、インテルのAdvanced Matrix Extensions(AMX)をサポートする全く新しいGolden Goveマイクロアーキテクチャに加えて、CPUはPCIe Gen 5、CXL 1.1プロトコル、DSAアクセラレータも対応する予定です。コア数、クロック、歩留まりを向上させるために、Sapphire Rapidsもチップレット設計を採用すると予想されているが、Intelによって確認されていません。

関連ニュース

Tom's Hardware・2022-06-03

Tom's Hardware・2022-06-03

Tom's Hardware・2022-06-03

Tom's Hardware・2022-06-01

Tom's Hardware・2022-05-31

Tom's Hardware・2022-05-31

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)