IBMがナノシート技術を用いた世界初の2nmチップを発表、インテルとサムスンが恩恵を受ける

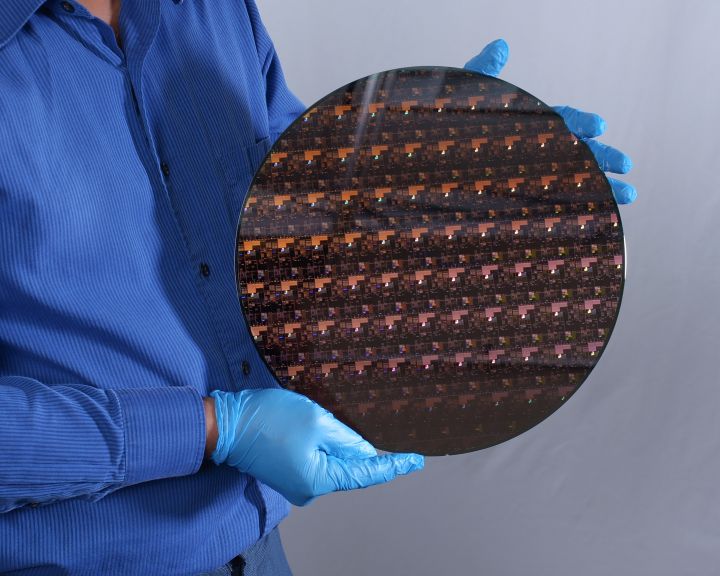

IBM Researchは本日、将来のプロセス技術の基盤となる、ナノシート技術を用いた新しい2nmチップを発表しました。IBMは、ニューヨーク州アルバニーの施設で、2nmのナノシートプロセスで製造された300mmのフルウェハーを展示しました。ただし、この技術はまだ研究段階であり、製品化可能なチップが入っているわけではありません。

IBMは現在、プロセッサの量産を行っておらず、インテルやサムスンなどのパートナー企業の技術開発を支援しています。インテルは最近、IDM 2.0の一環として、IBMと一緒に新しいプロセスノードとパッケージング技術を研究すると発表しました。つまり、インテルの将来の2nmチップは、IBMのブレークスルーのいくつかをベースにしている可能性があり、それはたくさんあります。

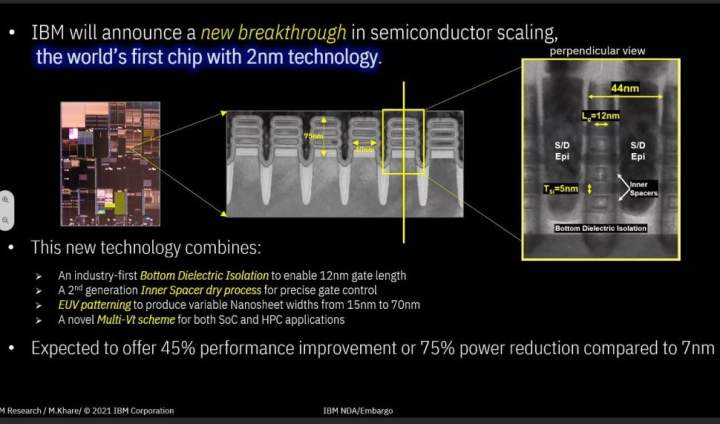

IBMは、この新しいプロセスノード技術によって、現在の7nmプロセスと同じ性能を維持しながら、同じ電力を使って45%の性能向上、または75%の電力削減が可能になると主張します。

IBM社によると、新しいチップには「指の爪ほどの大きさ」のチップに最大500億個のトランジスタが搭載されるとのことですが、他の最新チップと比較した場合のトランジスタ密度の指標(MTr/mm2)は提示されていません。

しかし、最近のチップのノード名の命名規則と同様に、「2nm」という指標は、チップ上の特定の物理的特徴とは関係ないことを覚えておく必要があります。2nmという指標は、チップ上の特定の物理的特徴とは関係なく、サードパーティのファウンドリが提供する同等のプロセスノードの消費電力と性能に基づいて開発されます。つまり、現代のチップのナノメートルという呼称は、ほとんどがマーケティングのためのものなのです。これは、IBMに限らず、業界全体の問題です。

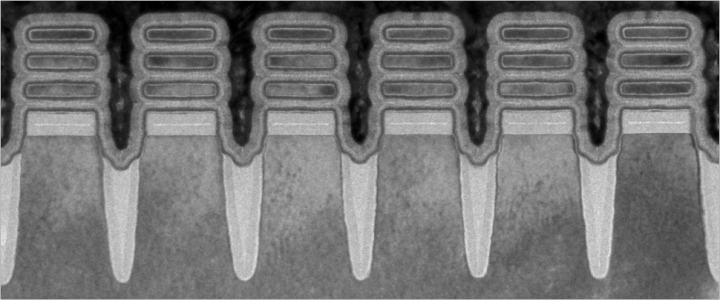

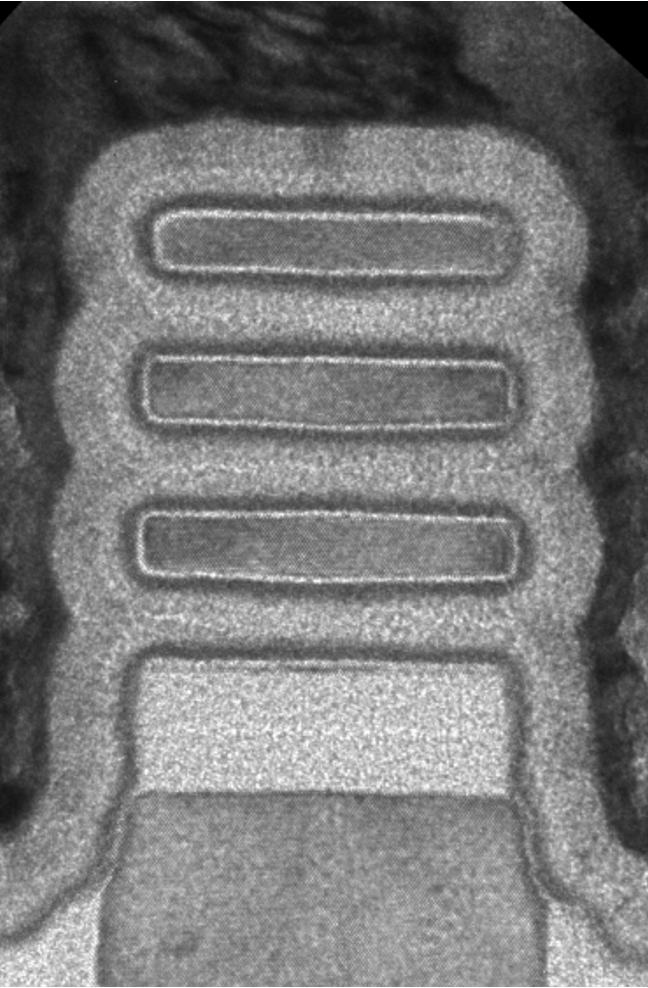

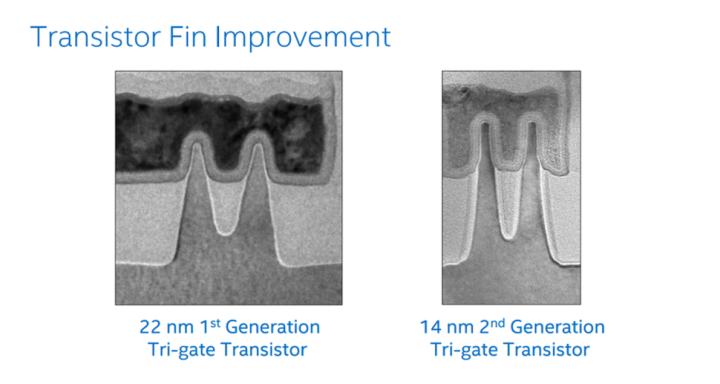

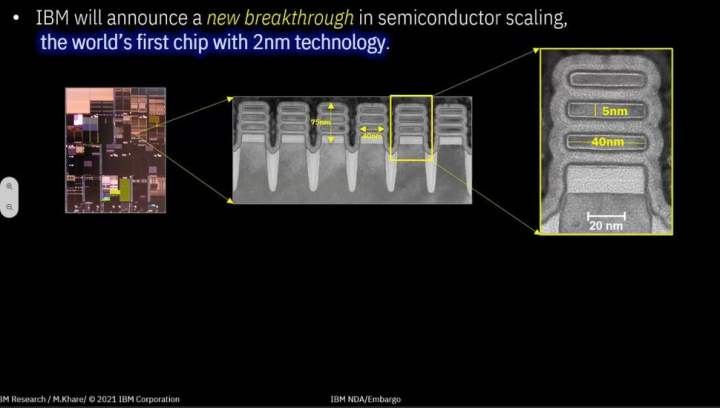

上のアルバムの1枚目の画像は、IBMの2nmトランジスタ6個の断面図です。電子顕微鏡でトランジスタの断面を見慣れている人なら、3枚目の画像がインテルの現行14nm FinFET技術であるのとは明らかに違うことがわかるだろう。

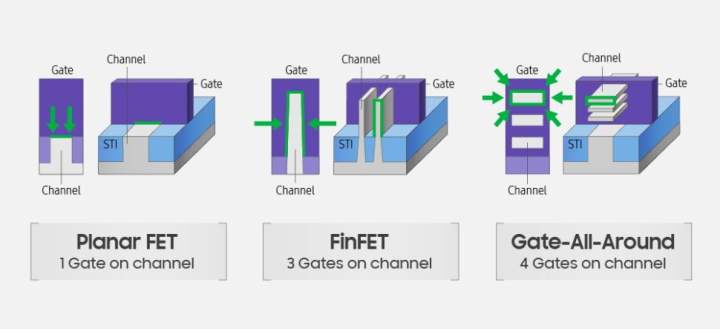

IBMの新設計では、シリコンナノシートを水平方向に3枚重ね、それぞれのナノシートをゲートで完全に囲んでいます。「ゲート・オール・アラウンド」(GAA)技術により、トランジスタのスイッチオフを妨げる電圧リークが低減されます。この問題は、FinFETトランジスタのように、ゲートがチャネルの三方を囲んでいても、トランジスタの微細化に伴って深刻化しています(最後の図)。

ここでは、IBMが発表した2nmのナノシートトランジスタに関するスライドと、さまざまな測定結果を見ることができます。各トランジスターは、ゲートに囲まれた3つのナノシート層が積層されており、スタック全体の高さは75nmです。各ナノシートのサイズは5nm×40nm、ゲート長は12nm、トランジスタのピッチは44nmです。

このほかにも、IBM社は、業界初のBottom Dielectric Isolationを採用してスタックの最初のナノシートからのリーク電流を排除し、12nmのゲート長を実現するなど、この技術でいくつかの注目すべき前進を遂げています。IBMは、2nmプロセスで使用している材料について、シリコン・ゲルマニウムを使用しているかどうかなどの詳細を明らかにしていませんが、将来的にはより詳細な情報を提供します。

また、IBMの2nmプロセスでは、トランジスタとそれに付随する構造物(ナノシートやゲート)を作成するFEOL(Front-End-of-Line)部分に、初めてEUVリソグラフィを採用します。一方、現在出荷されているトランジスタ技術では、チップ内の配線部分を構成するMOL(Middle-of-Line)、パッケージ部分を構成するBEOL(Back-end-of-Line)の段階でEUVパターニングを行っています。

驚くべきことに、IBMはFEOLを含むチップのすべての重要な層にシングルエクスポージャーのEUVを使用しており、マルチパターニングに比べて複雑さ(オプティカルマスクやステップ数の減少)と歩留まりの向上を実現しているという。この技術は、15nmから70nmまでのナノシート幅を作り出すことができるため、ファブでは様々なデザインターゲットに基づいてセルライブラリやSRAMを柔軟に作ることができます。また、IBM社は、2nmのテストウェーハの製造にASML社のEUV装置Twinscan NXE:3400Bを使用していることを明らかにしました。

IBMは、2014年にGlobalFoundries社にチップ製造施設を売却するまでの約25年間、自社でチップ製造施設を運営してきました。しかし、IBMは、製造施設を売却した後に始めた30億ドル規模の「Seven Nanometers and Beyond」研究プログラムを通じて、独自の研究開発とコア技術のライセンス供与を続けてきました。サムスンは同社の重要なパートナーであり、この関係はIBMのプロセス技術で今後も継続されます。実際、サムスンは今年、IBMと共同で開発した7nmプロセスで、IBM独自のPower10プロセッサーを生産する予定です。

インテルがIBMと将来のロジック技術やパッケージング技術で協力していくことを発表したのは、1ヶ月ちょっと前のIDM2.0の発表の中では控えめな過不足のない発言でした。しかし、このパートナーシップは、長年のプロセス技術の停滞からの回復を目指すインテルにとって非常に重要な意味を持ち、IBMは我々のブリーフィングで、同社の新しい2nm技術がインテルを含むすべてのパートナーに利益をもたらすものであることを明確に述べました。

IBMは、2nmのナノシート設計の基本的な詳細を明らかにしただけであり、トランジスタの小型化を進める上で重要な障害となっているインターコネクトのスケーリングにどのように取り組む予定なのかなど、まだ多くの情報があります。簡単に言えば、世界最小のトランジスタでも配線ができなければ意味がなく、この点が微細化を進める上で最も差し迫った制約となっています。

さらにIBMは、SRAMの詳細や、さまざまなセルライブラリの密度指標、2nmノードで使用する材料などを明らかにしていません。しかし、この技術を使った最初の製品が登場するまでには、これらすべての疑問、そしてできればそれ以上の疑問が解決されることを期待しています。IBMによると、2nmのナノシートプロセスは2024年後半にパートナーファウンドリーから展開される予定ですが、どのファウンドリーが研究成果に基づく技術をリードするかについての明確な予測は示していません。

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)