DRAMの代替品を開発。4倍の集積度で高速・低消費電力化を実現

NANDメモリーを開発した増岡富士夫氏が率いるUnisantis Electronics社は、ダイナミック・ランダム・アクセス・メモリー(DRAM)に比べて4倍の高密度、高性能、低消費電力を実現する揮発性メモリー、ダイナミック・フラッシュ・メモリー(DFM)を開発しました。

DRAMメモリは、データビットごとに1つのキャパシタと1つのトランジスタで構成される電荷貯蔵セルのアレイを使用しています。コンデンサは、1が記録されるとトランジスタを充電し、0が記録されるとトランジスタを放電します。アレイは、横方向にワードライン、縦方向にビットラインが配置されます。各列のセルは、2本の「+」と「-」のビットラインで構成され、それぞれのビットラインには、セルとの間でデータの読み書きを行うためのセンスアンプが接続されます。読み出しと書き込みの両方の操作はワードライン上で行われ、単一のビットをアドレス指定することは不可能です。

DRAMの歴史の中で、メーカーはDRAMの大容量化、低消費電力化、高性能化のために、新しいセル構造やプロセス技術を適用してメモリセルを小型化することに注力してきました。

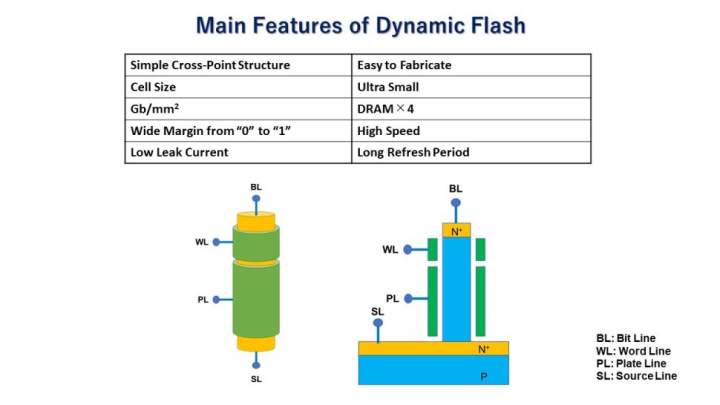

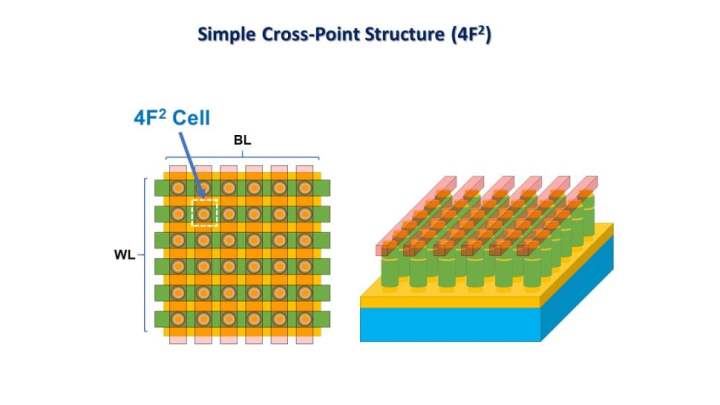

ユニサンティスのダイナミックフラッシュメモリは、デュアルゲートサラウンドゲートトランジスター(SGT)を採用してキャパシタを排除し、4F2ゲインセル構造(現在のDRAMが採用している6F2よりも小さい)を採用することで、DRAMと比較してメモリのビット密度を大幅に向上(最大4倍)させます。DFMは、業界初のキャパシタレスタイプのランダムアクセスメモリ(RAM)ではありませんが、過去の試みは失敗に終わりました。

ユニサンティス社によると、(1と0の間のマージンが狭すぎた)ZRAMとは異なり、同社のDFMは「1」と「0」のマージンの結果を大幅に増やし、速度の向上とメモリセルの信頼性の向上を実現します。DFMはPL(Plate Line)ゲートを用いて、「1」の書き込みモードと「0」の消去モードを分離することで、FB(Floating Body)を「安定化」させている、とユニサンティス社は言います。

Unisantis社はIPライセンス会社であり、メモリの生産や技術の商業化は行っていません。同社のDFMが市場に出てくるのは、ユニシャンティスが業界(すなわちSoCメーカーやメモリーメーカー)を説得して、同社のダイナミックフラッシュメモリーを採用させることができた場合に限られます。DFMは、従来のCMOS材料を使用し、高度な製造方法を必要としないため、実際に商品化される可能性があります。一方、同社のSGT(Dual Gate Surrounding Gate Transistor)IPは、GAAFETタイプのトランジスタを利用したいと考えている各方面からライセンスされる可能性があります。

DFM技術は、今月初めに開催された第13回IEEE International Memory Workshopにおいて、発明者である佐久井孝治博士と原田望博士によって発表されました。

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)