Ascenium社は、CPUを再発明し、命令セットを完全に破壊しようとしている。

Ascenium社は、CPUや汎用コンピュータの設計分野で注目を集めている新興企業のひとつです。Ascenium社のCEO兼共同設立者であるピーター・フォーリーは、かつてApple IやApple IIといったコンピュータの開発に携わり、多くのハードウェアデザイン関連企業で活躍してきました。Asceniumは最近、シリーズAで1,600万ドルの資金を調達しましたが、これは明らかに同社のミッションを確信している信号です。その使命とは、一体何なのでしょうか?

それは、初のSoftware-Defined Processorによって、パフォーマンスと電力効率の両方で既存のCPUアーキテクチャを凌駕することです。

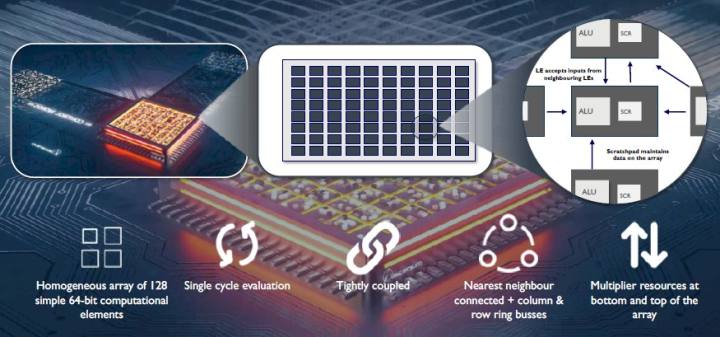

Ascenium社は、Aptosプロセッサにおいて、ソフトウェアとハードウェアの完璧な融合を実現することで、これを実現したいと考えています。Aptosプロセッサは、現在の最高性能のCPUに見られる深いパイプラインを排除し、LLVMコンパイラアーキテクチャをベースにした、真のコンパイラ駆動型並列処理CPUを実現します。現在、同社が開発しているAptosプロセッサーは、64ビット対応の128コアアレイの汎用単純コアをベースにします。Intel社のXeon Phiアーキテクチャへの取り組みを思い出していただければ、Ascenium社のAptosは、基本的には同じメニーコア設計のパラダイムですが、x86命令セット(およびそのコア設計上の制限と要件)を使用せず、ハードウェアリソース全体でワークロードを並列化する高性能のコンパイラを採用します。

Ascenium社は、アーキテクチャとソフトウェア設計に関する9つの特許をすでに取得しており、x86やArmなどの現行の命令セットを放棄しない、あるいは放棄できない、既存のコンピュータ大手に対する必要な防御手段を提供します。また、我々が現在知っている、50年前に作られた既存のISAを脅かすのに十分な製品を持っている新興プレイヤーを狙う可能性もあります。

ディープパイプライン(現在の問題に対する解決策が生み出されるまで、CPUアーキテクチャ内で命令が通るルートのこと)は、ワークロードの直列化では性能を向上させることができますが、並列化(つまり高性能化)が可能な多くのシナリオを否定することになります。また、深いパイプラインと、現代のCPUの処理を構成する特殊なハードウェアレジスタとステージにより、Ascenium社の推定では、命令の約50%がパイプラインを介したデータの移動に関連しており、処理時間と電力予算の両方を占める命令と移動となります。アーキテクチャに組み込まれたコンパイラベースのソフトウェアソリューションのアイデアは、理論的には、Aptosプロセッサが作業負荷の命令を解釈し、並列化される作業量が理論的な最大値に限りなく近くなるように処理リソースに分配することを可能にしますが、一方で、命令ベースのプロセッサよりもアーキテクチャの非効率性がはるかに少ないという利点があります。Ascenium社は、より高い消費電力/性能比を追求することを計画しています。そして、方程式において10%の節約であっても、ハイパースケーラーや、Ascenium社が最初にエコシステムに誘いたいと考えているデータセンターの顧客にとっては金になります。彼らこそが、このようなアーキテクチャから最も恩恵を受けることができるのです。

当然のことながら、データを移動させる必要性を減らすアーキテクチャを構築できれば、電力効率の面でもメリットがあります。しかし、x86には構造的な弱点があり、わずかな性能向上のためにも、膨大な量のトランジスタを投入しなければなりません。

そこでAscenium社は、命令セットを廃止し、命令セットやアーキテクチャに依存しない世界初のホモジニアスなプロセッサを開発し、新たなプロセッシングアーキテクチャを一から構築することを計画しています。これらは高い目標であり、そのリスクは計り知れません。しかし、それと同時に報酬も大きいのです。

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)