2025年までのインテルのプロセスロードマップ。プロセスノードの名称変更、オングストローム時代の幕開け

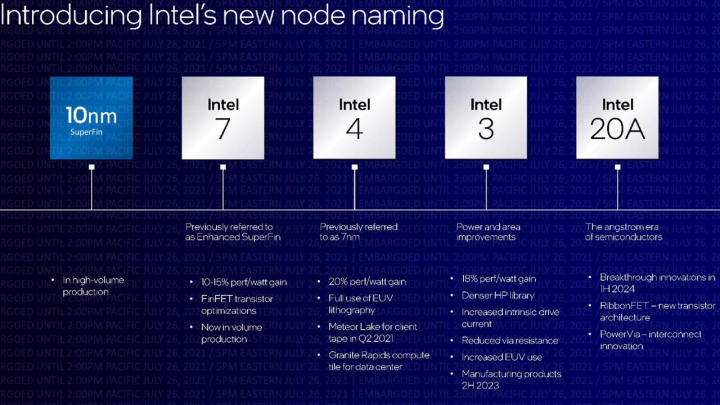

Intel社のCEOであるパット・ゲルシンガー氏は、2025年までの新しいプロセスおよびパッケージングのロードマップを発表しました。このロードマップでは、標準的なナノメートルスケールの技術からオングストロームクラスの非常に小さなトランジスタまで、将来のプロセスノードを毎年順次発表していく予定となります。また、10年前に登場したFinFET以来の新しいトランジスタデザインであるRibbonFETや、トランジスタを配線の間に挟み込む新しい裏面電源供給技術であるPowerViaなど、オングストロームクラス(ナノメートルの次の単位)の技術の最初の詳細が発表されました。また、インテルは、TSMCなどの外部ファウンドリーが使用する名称に合わせて、プロセスノードの名称を再度変更します。再ブランド化は、インテルの10nm Enhanced SuperFinから始まり、今後は「インテル7」と改称されます。

インテルは、そのプロセス技術が2024年までに現在の業界リーダーであるTSMCと同等になり、2025年までには「プロセス性能のリーダー」を奪還するとします。これは、次世代チップのためにASML社から次世代高NA EUV装置を最初に導入したことも貢献します。また、インテルは、「Intel Accelerated」ウェブキャストにおいて、将来のFoveros OmniおよびDirect技術の詳細を発表し、Sapphire Rapidsチップが業界初の「デュアル・レチクル・サイズのデバイス」になることを発表しました。

AWSはインテルのパッケージングサービスを利用することを発表し、Qualcommはインテルの20Aプロセスを今後のチップ設計に利用することを発表しました。それでは、早速見ていきましょう。

インテル、10nmを7nmに改名

ロードマップを紹介する前に、インテルは、TSMCやサムスンなどのサードパーティファウンドリーが使用している現在の名称規則に合わせて、プロセスノードの名称を変更することになりました。

新しい方針は、Alder Lakeプロセッサでデビューする予定の10nm Enhanced SuperFinプロセスと呼ばれていたものから始まります。インテルがこのプロセスノードを発表したのはかなり前のことで、すでに量産体制に入っています。

インテルは、次の10nmノードを「インテル7」と改称し、「ナノメートル」という名称を廃止するため、同社のプロセスノードに従来のような「nm」という接尾語が付けられることはなくなります。その代わりに、インテルは性能、消費電力、面積の進歩に基づいてノードを命名します。その結果、インテルの歴代のノード名もすべて調整され、インテルの7nmが「インテル5」になるなどの調整が行われることになります。

今回のノード名の変更は、インテルがIDM 2.0の一環として他社のチップを製造するインテル・ファウンドリ・サービシズ(IFS)事業を構築するためのものです。インテルのIFSは、TSMCやSamsungと直接競合することになりますが、ノードの命名規則がすでに破られたことを考えると、業界の他の企業に合わせることは十分に意味のあることです。

しかし、「バニラ」の10nm SuperFinがすでに出荷されている中で、10nm Enhanced SuperFinの名称を変更することは、全く新しいノードを待って変更するよりも理想的ではないことは間違いありません - このアプローチは紛らわしいことは間違いありません。いずれにしても、Intelはいずれかの時点で名称変更による批判を受けなければならず、次のチップラインでそれを選択したことになります。この話題については、記事の後半でもう少し詳しく紹介します。

インテルプロセスロードマップ 2021 - 2025

インテルの以下のロードマップは、Tiger Lakeプロセッサなど、現在一部の製品で出荷されている10nm SuperFinから始まります。しかし、上述したように「Intel 7」は、IntelがすでにAlder LakeやSapphire Rapidsチップを搭載すると発表した10nm Enhanced SuperFinプロセスと同じもので、名前が変わっているだけです。

同様に、先日延期を発表したインテルの7nmは、現在「インテル4」というブランド名になりました。ロードマップの残り2つのエントリーは、まったく新しいものです。

インテルは、「10nm Enhanced SuperFin」と呼ばれていたプロセスである「インテル7」を、クライアント向け(Alder Lake)は今年中に、データセンター向け(Sapphire Rapids)は2022年の第1四半期に出荷するとします。インテルによれば、「インテル7」は、前身の10nm SuperFinに比べて、ワット当たりの性能が10~15%向上します。

通常であれば、それはピーク性能の向上(効率を犠牲にして)か、効率の向上(性能を犠牲にして)のどちらかになりますが、両方を同時に実現することはできません。注目すべきは、電圧/周波数カーブの上限で必要な電力が増加するため、性能の向上は直線的には拡大しないということで、Intel 7が10nm SuperFinよりも15%速くなることはないでしょう。

一方、Intel 4(旧7nm)は、2022年後半には「生産準備が整う」としながらも、2023年前半には製品として市場に投入されます。インテルによれば、このノードでは、前世代と比較してワット当たりの性能が20%向上し(上記のルールが適用されます)、EUV技術を全面的に採用します。これは重要な前進であり、インテルがEUV製造の採用を遅らせていることが、10nmの遅れの大きな要因であると考えられます。

Intel 4プロセスを採用したチップは2023年に登場する予定で、前半にはクライアント向けのMeteor Lakeプロセッサ、後半にはサーバー向けのGranite Rapids製品が登場します。スケジュールでは、TSMCやSamsungといったインテルの競合企業が、2023年の時点でプロセスノードの優位性を保っていることになります。TSMCは、2023年には3nmノードのフル生産に入ると予測しており、インテルが引き続き一部の製品を外注する必要があることを説明します。インテルは、自社のパッケージング技術と分離型設計思想を活用して、外部で生産されたTSMCのチップを自社製品に統合することで、遅延を回避することを計画します。

全く新しい「インテル3」は、2023年後半に製品に姿を現すと、「インテル4」に比べてワット当たりの性能が18%向上します。「インテル3」は、同じ年の初めに遅れる「インテル4」に続く、信じられないほど高速な製品です。しかし、インテルは、初期のモデリングとテストチップのデータに基づいて、"インテルにとって、あるいは他のベンダーにとって、標準的なフルノードよりも高いレベルの改善 "であることを確認します。

インテルは、2024年の前半にまったく新しい時代を迎える予定です。オングストロームの時代です。オングストローム時代とは、物理的な特性をナノメートル(10億分の1メートル)単位で正確に測定できなくなる時代のことです。オングストロームは、1メートルの100億分の1の単位で、正確に測定できるようになります。インテルの最初のオングストロームクラスのプロセスは、20A(Aはオングストローム)として登場し、インテル初のゲート・オール・アラウンド(GAA)トランジスタであるRibbonFETと、非常に小さなトランジスタに電力を供給するための新しいアプローチであるPowerViaを搭載します。

Intel Angstroms、RibbonFET、PowerVia

RibbonFETは、インテルにとって初のゲート・オール・アラウンド(GAA)デザインであり、2011年に発表されたFinFET以来、初めての新しいトランジスタデザインとなります。この設計では、4枚のナノシートが積層され、それぞれがゲートで完全に囲まれます。この設計により、複数のフィンと同じ駆動電流を使用しながら、より小さな面積でトランジスタのスイッチングを高速化できます。競合他社もGAA方式を採用していることからも、その可能性は高いと言えるでしょう。

インテルはRibbonFETについてまだ多くの情報を公開していませんが、IBMが最近発表したGAA/ナノシート技術に酷似しており、2nmのテストウェハで製造されます(以下の画像)。インテルは先日のIDM 2.0の発表で、将来のロジックおよびパッケージング技術についてIBMと協力することを発表しており、これは非常に重要な意味を持ちます。提携は、インテルが長年のプロセス技術の停滞からの回復を目指す上で重要です。IBMとの研究成果に関するブリーフィングでは、同社の新しい2nm技術がインテルを含むすべてのパートナーに利益をもたらすものであることが明確に示されました。IBMの同様の技術については、こちらをご覧ください。

IBMのナノシート/GAA技術を紹介した際にも述べましたが、世界最小のトランジスタであっても配線ができなければ意味がありませんし、この点は小型化を進める上で最も差し迫った制約の1つとなります。

インテルの新技術「PowerVia」は、インターコネクトの問題を解決する有望なアプローチと言えそうです。PowerViaは、トランジスタに供給されるすべての電力を、トランジスタの裏面を通して直接トランジスタに供給します。これにより、電力供給をトランジスタの裏面に分離し、データ伝送用のインターコネクトは従来通り反対側に配置します。インテルによると、電源回路とデータ伝送用のインターコネクトを分離することで、電圧降下特性が改善され、トランジスタのスイッチングが高速化されるとともに、チップ上面での信号配線の高密度化が可能になるという。また、配線を簡素化することで、抵抗や容量を減らした高速な配線を使用できるため、信号処理にもメリットがあります。

しかし、この技術には当然ながら多くの課題があります。例えば、電力供給回路が絶縁層となってトランジスタの熱を逃がさないようにすることです。これらの課題に、インテルがどのように取り組んでいくのかが注目されます。

インテル18Aと高NA EUV

インテルはロードマップに含めていませんが、すでにオングストロームクラスの次世代プロセスの開発を進めており、RibbonFETトランジスタを強化した「インテル18A」が「2025年初頭」に計画されます。

インテルの18Aは、高NA EUVを使用するための変曲点となるでしょう。高NA EUVとは、現行のマシンよりも小さな解像度(8nm未満)でデザインをエッチングできる、新しい超精密バージョンのEUVマシンのことです。既存のEUV装置では、あまり望ましくないマルチパターニングEUV技術が必要とされますが、このような微細な形状でシングルパターニングEUVを行うためには、これらの装置が必要となります。

インテルは、ASML社からHigh NA EUV装置の提供を受ける最初の企業になるとしており、10nmの時のようにTSMC社に遅れをとるのではなく、次世代のEUV装置でリードしていく方針を示します。注目すべきは、インテルは高NA EUV装置を最初に受け取るとは言ったものの、高NA EUVによる大量生産に最初に参入するとは言っていないことです。

インテルは、最先端のインテル3と、それに続く20Aや18Aなどのノードを、ファウンドリの顧客に提供すると語ります。つまり、Intel 3の生産開始は2023年後半になるため、今のところIntelはファウンドリー顧客にトレイリングエッジのノードを提供することにとどまると思われます。

インテルの概要によると、2024年には業界トップのTSMCとプロセス性能が同等になり、2025年にはトップに立ちます。しかし、インテルの脚注には、これがトランジスタの性能や密度ではなく、1ワットあたりの性能に基づくものであることが明記されます。

なお、このパリティ・ステートメントは、インテルのプロセス技術にのみ適用され、最終製品には適用されません。インテルは今後2025年までの間、新しいマイクロアーキテクチャーや、さまざまな技術をより効率的に結びつけるパッケージングのイノベーション(詳細は後述)、さらには史上初めて最高級チップの設計の一部を外部に委託するなどして、「リーダーシップ製品」で競争していく計画です。インテルは、コンシューマー向けとデータセンター向けの「CPUリーダーシップ」チップを、2023年にTSMCの未指定のノードでリリースするとします。

インテルパッケージングアップデート

Intel社のパッケージングのアップデートは、もう少しスパルタンなものでした。インテルは、Sapphire RapidsプロセッサーにEMIBパッケージ技術を採用することを発表しました。EMIBパッケージ技術とは、複数のダイを接続するためにパッケージに組み込まれたシリコンブリッジを使用するもので、このインターコネクト技術を採用した初のデータセンター製品となります。すでにSapphire Rapidsの写真が公開されているため、これはちょっとした公然の秘密となりました。ただし、次世代EMIBのバンプピッチを55ミクロンから45ミクロンに変更することを明らかにしました。

インテルの3次元チップ積層技術「Foveros」は、同社が最近引退したLakefieldプロセッサーでデビューしましたが、次世代のFoveros実装は、インテルの次期Meteor Lakeプロセッサーでデビューします。この世代のFoverosは、36ミクロンのバンプピッチに向上します。

インテルの次期Foveros Omniは、さらに一歩進んだものです。相互接続技術は、相互に接続されたダイの周辺部にある銅製の柱で電力を供給し、ダイの中心部にあるTSV接続でチップ間のデータをシャッフルするというものです。これは初代Foverosとは異なり、データと電力の伝送を分離することで、電力とデータの両方の信号をすっきりと配線することができます。これにより、25ミクロンの狭いバンプピッチが可能になり、異なるベースダイを混ぜ合わせることができるようになりました。この技術は、インテルのODIパッケージ技術と基本的に同じです。

また、インテルは、ハイブリッドボンディング技術をFoverosパッケージングと組み合わせて新たな用途に使用します。Foveros Directは、標準的な熱圧着の代わりに、ダイ・オン・ウェハのハイブリッドボンディング(銅と銅の接合)を活用します。新技術は、10nm以下の積極的なバンプピッチを採用しており、相互接続密度の向上、相互接続回路の簡素化、抵抗値と消費電力の低減を実現するとともに、広帯域化にも対応します。インテルは、すでにハイブリッド・ボンディングを採用したスタックドSRAMチップをテープアウトしており、今回、この技術をFoverosインターコネクトに適用することになりました。しかし、この技術がいつ市場に登場するかは明らかにされていません。

インテル、プロセスノードの名称を変更 - 続き

インテルがプロセスノードの名称を変更したことには、多くの批判が寄せられるだろうが、これは必要悪です。1997年当時のインテルのプロセスノードの命名は、トランジスタのゲート長(またはM1ハーフピッチ)をベースにしたシンプルなものだったが、物理的な測定値と実際のノード名との相関関係は時とともに変化していました。実際、FinFETトランジスタの登場により、両者の相関関係は完全になくなってしまいました。現在、インテルのノード名の変更は、新技術の導入かトランジスタ密度の増加に伴って行われます。

ナノメートルというと、半導体にとっては小さい方がいいことは誰でも知っています。しかし、インテルが物理的な測定方法から徐々に名前を変えていったのに対し、TSMCやサムスンなどのサードパーティのファウンドリーは、基礎となる技術の単純な変更に基づいて、より根本的な調整を行いました。例えば、平面トランジスタからFinFETトランジスタへの移行は、トランジスタ密度の向上につながらない場合でも、名称変更を余儀なくされました。PDK/BKM(Product Design Kit/Best Known Method)の変更でさえ、サードパーティファブにとっては、プロセスに新しい番号を割り当てるのに十分な口実となり、命名規則は、物理的な測定に結びついた指標というよりも、マーケティング活動に近いものとなります。

そして、サードパーティファウンドリはマーケティング戦争に勝利します。しかし、現実の世界では、トランジスタ密度、ピーク性能、1ワットあたりの性能、さまざまな種類のロジック/回路、SRAMの集積度など、さまざまな要因がプロセスノードの経済性や性能に影響を与えます。

インテルが10nmノードで失敗し、一連の「+」リビジョンとそれに続く3つのノードの遅延を引き起こしたことで、インテルがプロセスのリーダーシップをTSMCに譲り、ノードの名称問題は悪化しました。現在、TSMCが3nmプロセスを最初に出荷する時期によって、TSMCはインテルを1ノードまたは2ノードリードすることになります。特にインテルにとっては、プロセス技術がTSMCに遅れをとっていることに加えて、ネーミングも遅れているため、TSMCのリードの大きさを誤魔化していることになります。インテルの10nmはTSMCの7nmに似ており、インテルの7nmはTSMCの5nmに似ています。

また、インテルは、業界の他の人々がノードのネーミングはもはや実際の技術とは何の相関もないと指摘していることを裏付ける引用文(上のアルバムにある)も紹介します。(上のスライドでは、インテルの7nmはTSMCの3nmに近いとしますが、これは大目に見てください)。)

ファウンドリ市場でTSMCやSamsungとの競争が激化している現在、Intelが新しいネーミングに移行することは理にかなっているが、7nm(現在はIntel 4と呼ばれている)を待たずに10nm世代で移行することを選択したことには驚きます。インテルはすでに「+」のネーミングから「Enhanced SuperFin」のようなフルネームに移行していることを考えると、今回の新しいネーミングは、すでに発売されている製品に適用されるため、同社の進捗状況を解釈する上で、また新たな混乱を招くことになります。インテルがしばらくの間、この命名規則とロードマップを守ってくれることを期待しよう。

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)