ZeroPoint Technology AB、ハードウェアベースのRAMデータ圧縮で250万ドルを獲得

チャルマース工科大学からスピンアウトしたスウェーデンの新興企業、ZeroPoint Technologies ABは本日、最新作を発表しました。特許と250万ユーロ(300万ドル弱)のシード資金を獲得したメモリ技術「Ziptilion」は、高い電力効率を実現しながら、RAMの容量と帯域幅を倍増させることを約束します。

皆さんの中には、80年代から90年代にかけて存在した古いRAM倍増ソフトを覚えている方も多いと思います。このソフトウェアを購入したユーザーは、適切なハードウェアのアップグレードをしなくても、RAM容量を2倍にすることができると約束されており、当時は大きな詐欺でした。しかし今日、ZeroPoint社は、まったく異なるハードウェアベースのアプローチでそれを実現しようとします。

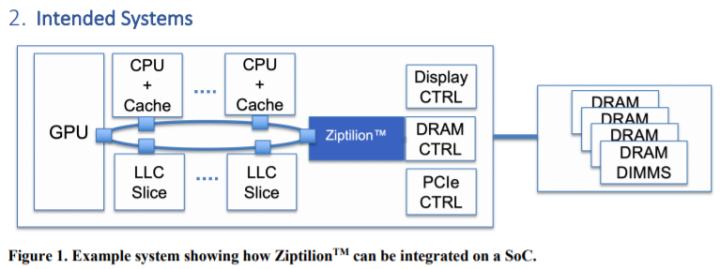

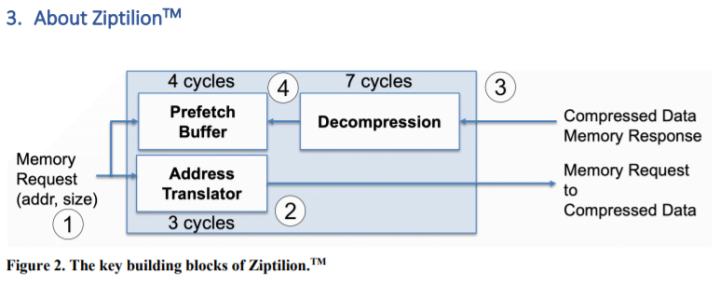

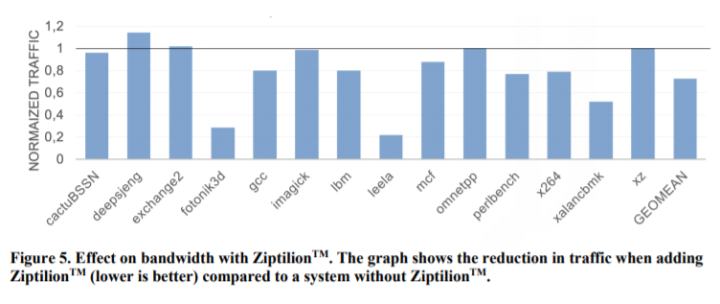

Ziptilionと名付けられたこのハードウェアIPは、独自の圧縮アルゴリズムを用いてメモリデータを圧縮することで機能し、ZeroPoint社は2〜3倍の帯域幅の増加を主張します。Ziptilionの仕組みは、IPをデザインに組み込むことで、業界標準のSoC AXIインターコネクトファブリックを使用して、メモリコントローラやプロセッサのキャッシュサブシステムと直接連携させるます。同社は、Ziptilion IPが圧縮されたデータをメモリとの間でフェッチする際に、Ziptilion IPを使用することでメモリのレイテンシーがほとんど短縮されるほど、効率的な方法でメモリを圧縮できるとします。極端なケースでは、レイテンシーが約1〜100ナノ秒高くなることもありますが、デメリットよりもメリットの方が大きいのです。

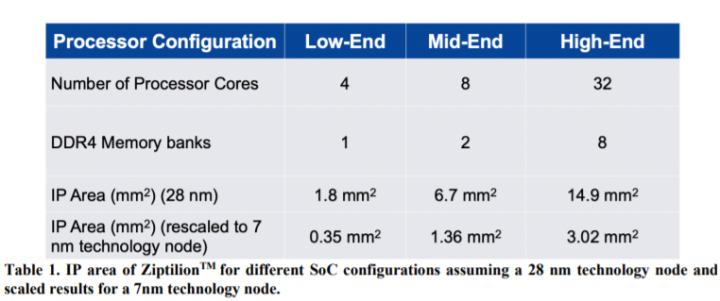

このIPのコストはどれくらいなのだろうか?同社によると、TSMCの28nmノードでは、Ziptilion IPを周波数800MHz、帯域幅32GB/sのAXIバスに実装したデザインが存在します。このIPを使用した平均的な7nmデュアルチャネルメモリデザインでは、ダイ使用量が1.36平方ミリメートルしか増加しませんが、8チャネルのメモリコントローラを搭載したサーバーCPUでは、このIPを組み込むために3.02平方ミリメートルの追加が必要になります。

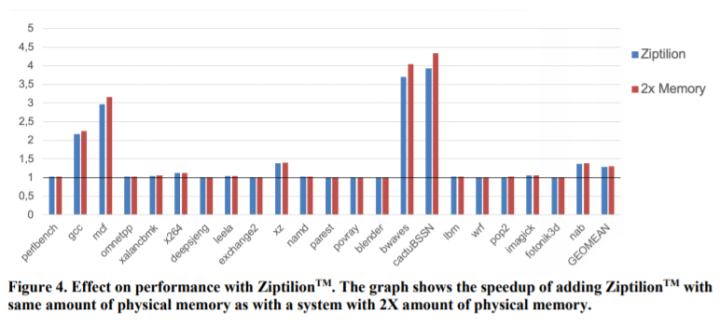

性能面では、Ziptilion IPのホワイトペーパーで、その圧縮技術とRAMの増設を比較します。正確には、システムのRAM容量を2倍にした場合と、ZiptilionデザインをSoCに追加した場合の影響を比較します。ホワイトペーパーでは、Ziptilion IPの圧縮技術が、システムのRAM容量を2倍にした場合と、SoCにZiptilionデザインを追加した場合の影響を比較します。

また、可能なアプリケーションについては、設計はさまざまな形で実装することができます。具体的には、Raspberry Piに搭載されるようなSoCや、スマートフォンのSoCでは、搭載されるシステムメモリに制限があるため、IPブロックの恩恵を大きく受けることができます。例えば、8GBのRAMを搭載したシンプルなスマートフォンでも、IPブロックを利用することで、16GBのRAMにアップグレードすることができます。

この技術がメインストリーム市場に登場するかどうかはわかりませんが、かつてのRAMダブラーとは異なり、将来性のある技術です。この技術を開発した人々は、15年以上にわたってメモリ圧縮アルゴリズムを研究してきましたが、ようやく市場がこのような技術を将来の設計に組み込む準備ができたようです。

みんなの自作PC

![[70万]RTX3080 12900K 搭載エヴァコラボゲーミングPC(でも正直70万あったら3090Ti乗せてもおさまるから見た目追い求める人以外は3090Ti買ったほうがいい)](https://cdn.jisaku.com/upload/7c/noRgcuZik3ymkn/280.jpg)